# Intel® IA-64 Architecture Software Developer's Manual

Volume 4: Itanium<sup>™</sup> Processor Programmer's Guide

Revision 1.1 July 2000

Document Number: 245320-002

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel® IA-64 processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's website at http://developer.intel.com/design/litcentr.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

# int<sub>e</sub>l。 Contents

| 1 | Αbοι  | ut this Manual                                              | 1-1 |

|---|-------|-------------------------------------------------------------|-----|

|   | 1.1   | Overview of Volume 1: IA-64 Application Architecture        | 1-1 |

|   |       | 1.1.1 Part 1: IA-64 Application Architecture Guide          | 1-1 |

|   |       | 1.1.2 Part 2: IA-64 Optimization Guide                      | 1-2 |

|   | 1.2   | Overview of Volume 2: IA-64 System Architecture             | 1-2 |

|   |       | 1.2.1 Part 1: IA-64 System Architecture Guide               |     |

|   |       | 1.2.2 Part 2: IA-64 System Programmer's Guide               | 1-3 |

|   |       | 1.2.3 Appendices                                            | 1-4 |

|   | 1.3   | Overview of Volume 3: Instruction Set Reference             | 1-4 |

|   |       | 1.3.1 Part 1: IA-64 Instruction Set Descriptions            | 1-4 |

|   |       | 1.3.2 Part 2: IA-32 Instruction Set Descriptions            | 1-4 |

|   | 1.4   | Overview of Volume 4: Itanium™ Processor Programmer's Guide | 1-5 |

|   | 1.5   | Terminology                                                 | 1-5 |

|   | 1.6   | Related Documents                                           | 1-6 |

|   | 1.7   | Revision History                                            | 1-6 |

| 2 | Reai  | ster Stack Engine Support                                   | 2-1 |

| _ | 2.1   | RSE Modes                                                   |     |

|   | 2.2   | RSE and Clean Register Stack Partitions                     |     |

| 3 | Virtu | al Memory Management Support                                | 3-1 |

| - | 3.1   | Page Size Supported                                         |     |

|   | 3.2   | Physical and Virtual Addresses                              |     |

|   | 3.3   | Region Register ID                                          |     |

|   | 3.4   | Protection Key Register                                     |     |

| 4 | Proc  | essor Specific Write Coalescing (WC) Behavior               | 4-1 |

|   | 4.1   | Write Coalescing                                            | 4-1 |

|   | 4.2   | WC Buffer Eviction Conditions                               | 4-1 |

|   | 4.3   | WC Buffer Flushing Behavior                                 | 4-2 |

| 5 | Mode  | el Specific Instruction Implementation                      | 5-1 |

|   | 5.1   | ld.bias                                                     | 5-1 |

|   | 5.2   | Ifetch Exclusive Hint                                       | 5-1 |

|   | 5.3   | fwb                                                         | 5-1 |

|   | 5.4   | thash                                                       |     |

|   | 5.5   | ttag                                                        | 5-2 |

|   | 5.6   | ptc.e                                                       | 5-3 |

|   | 5.7   | mf.a                                                        | 5-3 |

|   | 5.8   | Prefetch Behavior                                           | 5-3 |

|   | 5.9   | Temporal and Non-temporal Hints Support                     | 5-3 |

| 6 | Proc  | essor Performance Monitoring                                | 6-1 |

|   | 6.1   | Performance Monitor Programming Models                      |     |

|   |       | 6.1.1 Workload Characterization                             | 6-2 |

|   |       | 6.1.2 Profiling                                             | 6-5 |

|   |       | 6.1.3 Event Qualification                                   | 6-8 |

|   | 6.2   | Performance Monitor State                                                 |      |

|---|-------|---------------------------------------------------------------------------|------|

|   |       | 6.2.1 Performance Monitor Control and Accessibility                       |      |

|   |       | 6.2.2 Performance Counter Registers                                       | 6-16 |

|   |       | 6.2.3 Performance Monitor Overflow Status Registers (PMC[0,1,2,3])        | 6-17 |

|   |       | 6.2.4 IA-64 Instruction Address Range Check Register (PMC[13])            | 6-18 |

|   |       | 6.2.5 IA-64 Opcode Match Registers (PMC[8,9])                             | 6-20 |

|   |       | 6.2.6 IA-64 Data Address Range Check (PMC[11])                            | 6-21 |

|   |       | 6.2.7 Event Address Registers (PMC[10,11]/PMD[0,1,2,3,17])                | 6-22 |

|   |       | 6.2.8 IA-64 Branch Trace Buffer                                           | 6-27 |

|   |       | 6.2.9 Processor Reset, PAL Calls, and Low Power State                     | 6-31 |

|   |       | 6.2.10 References                                                         | 6-32 |

| 7 | Perfo | rmance Monitor Events                                                     | 7-1  |

|   | 7.1   | Categorization of Events                                                  | 7-1  |

|   | 7.2   | Basic Events                                                              | 7-1  |

|   | 7.3   | Instruction Execution                                                     | 7-2  |

|   | 7.4   | Cycle Accounting Events                                                   | 7-4  |

|   | 7.5   | Branch Events                                                             | 7-5  |

|   | 7.6   | Memory Hierarchy                                                          | 7-6  |

|   |       | 7.6.1 L1 Instruction Cache and Prefetch                                   | 7-7  |

|   |       | 7.6.2 L1 Data Cache                                                       | 7-8  |

|   |       | 7.6.3 L2 Unified Cache                                                    | 7-9  |

|   |       | 7.6.4 L3 Unified Cache                                                    | 7-10 |

|   | 7.7   | System Events                                                             | 7-10 |

|   | 7.8   | Performance Monitor Event List                                            |      |

| 8 | Mode  | I Specific Behavior for IA-32 Instruction Execution                       | 8-1  |

|   | 8.1   | Processor Reset and Initialization                                        | 8-1  |

|   | 8.2   | New JMPE Instruction                                                      | 8-1  |

|   | 8.3   | System Management Mode (SMM)                                              | 8-1  |

|   | 8.4   | Machine Check Abort (MCA)                                                 |      |

|   | 8.5   | Model Specific Registers                                                  |      |

|   | 8.6   | Cache Modes                                                               | 8-2  |

|   | 8.7   | 10-byte Floating-point Operand Reads and Writes                           |      |

|   | 8.8   | Floating-point Data Segment State                                         |      |

|   | 8.9   | Writes to Reserved Bits during FXSAVE                                     |      |

|   | 8.10  | Setting the Access/Dirty (A/D) Bit on Accesses that Cross a Page Boundary |      |

|   | 8.11  | Enhanced Floating-point Instruction Accuracy                              | 8-3  |

|   | 8.12  | RCPSS, RCPPS, RSQRTSS, RSQRTPS Instruction Differences                    |      |

|   | 8.13  | Read/Write Access Ordering                                                |      |

|   | 8.14  | Multiple IOAPIC Redirection Table Entries                                 |      |

|   | 8.15  | Self Modifying Code (SMC)                                                 |      |

|   | 8.16  | Raising an Alignment Check (AC) Fault                                     |      |

|   | 8.17  | Maximum Number of IA-64 Processors Supported in MP System                 |      |

|   |       | Running Legacy IA-32 OS (IA-32 system environment)                        | 8-5  |

# Figures

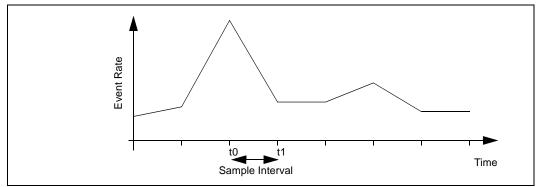

| 6-1  | Time-based Sampling                                                                         | 6-2  |

|------|---------------------------------------------------------------------------------------------|------|

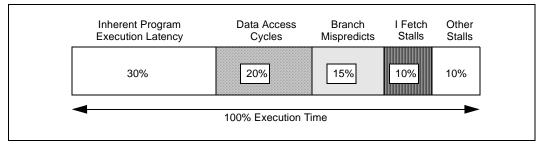

| 6-2  | IA-64 Cycle Accounting                                                                      |      |

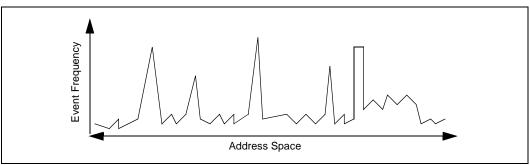

| 6-3  | Event Histogram by Program Counter                                                          | 6-6  |

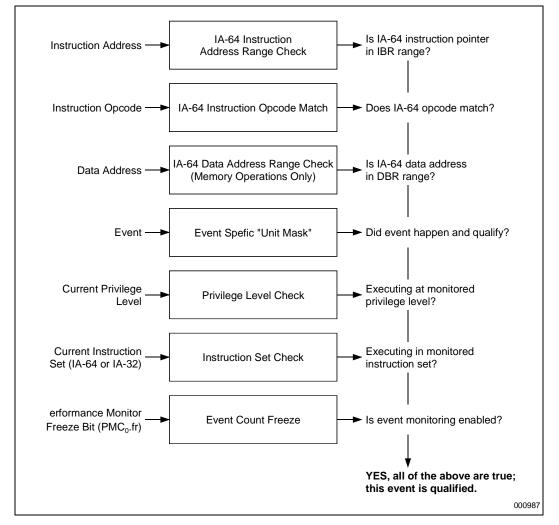

| 6-4  | Itanium™ Processor Event Qualification                                                      | 6-9  |

| 6-5  | Instruction Tagging Mechanism in the Itanium™ Processor                                     | 6-10 |

| 6-6  | Single Process Monitor                                                                      |      |

| 6-7  | Multiple Process Monitor                                                                    | 6-12 |

| 6-8  | System Wide Monitor                                                                         | 6-12 |

| 6-9  | Itanium™ Processor Performance Monitor Register Model                                       | 6-14 |

| 6-10 | Processor Status Register (PSR) Fields for Performance Monitoring                           | 6-15 |

| 6-11 | Itanium™ Processor Generic PMD Registers (PMD[4,5,6,7])                                     | 6-16 |

| 6-12 | Itanium™ Processor Generic PMC Registers (PMC[4,5])                                         | 6-16 |

| 6-13 | Itanium™ Processor Generic PMC Registers (PMC[6,7])                                         | 6-16 |

| 6-14 | Itanium <sup>™</sup> Processor Performance Monitor Overflow Status Registers (PMC[0,1,2,3]) | 6-18 |

| 6-15 | Itanium <sup>™</sup> Processor Instruction Address Range Check Register (PMC[13])           | 6-18 |

| 6-16 | Opcode Match Registers (PMC[8,9])                                                           | 6-20 |

| 6-17 | Instruction Event Address Configuration Register (PMC[10])                                  | 6-22 |

| 6-18 | Instruction Event Address Register Format (PMD[0,1]                                         | 6-23 |

| 6-19 | Data Event Address Configuration Register (PMC[11])                                         | 6-25 |

| 6-20 | Data Event Address Register Format (PMD[2,3,17])                                            | 6-25 |

| 6-21 | IA-64 Branch Trace Buffer Configuration Register (PMC[12])                                  | 6-28 |

| 6-22 | Branch Trace Buffer Register Format (PMD[8-15])                                             | 6-30 |

| 6-23 | IA-64 Branch Trace Buffer Index Register Format (PMD[16])                                   | 6-31 |

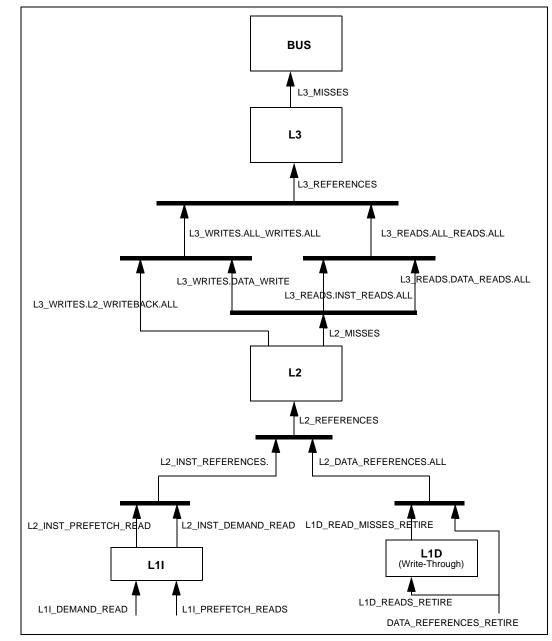

| 7-1  | Event Monitors in the Itanium <sup>™</sup> Processor Memory Hierarchy                       | 7-7  |

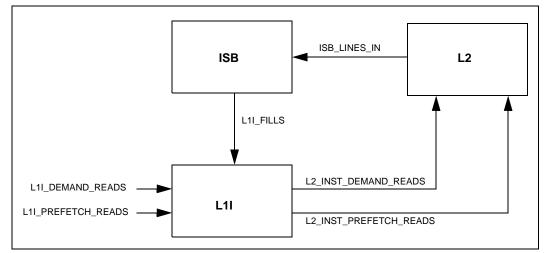

| 7-2  | L1 Instruction Cache and Prefetch Monitors                                                  | 7-8  |

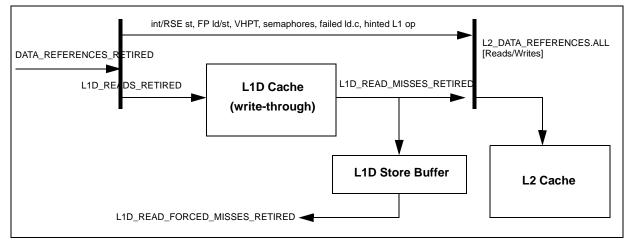

| 7-3  | L1 Data Cache Monitors                                                                      | 7-9  |

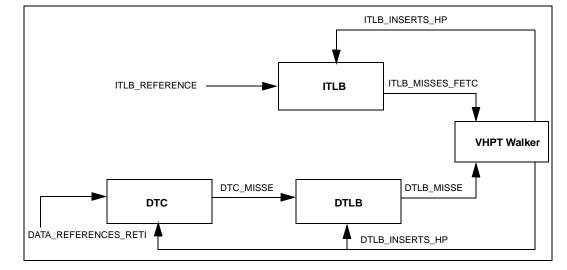

| 7-4  | Itanium™ Processor Instruction and Data TLB Monitors                                        | 7-12 |

# **Tables**

| 4-1  | Itanium <sup>™</sup> Processor WCB Eviction Conditions                                     | 4-1  |

|------|--------------------------------------------------------------------------------------------|------|

| 6-1  | Average Latency per Request and Requests per Cycle Calculation Example                     | 6-4  |

| 6-2  | Itanium <sup>™</sup> Processor EARs and Branch Trace Buffer                                | 6-7  |

| 6-3  | Itanium™ Processor Event Qualification Modes                                               | 6-10 |

| 6-4  | Itanium™ Processor Performance Monitor Register Set                                        | 6-15 |

| 6-5  | Performance Monitor PMC Register Control Fields (PMC[4,5,6,7,10,11,12])                    | 6-15 |

| 6-6  | Itanium™ Processor Generic PMD Register Fields                                             | 6-16 |

| 6-7  | Itanium <sup>™</sup> Processor Generic PMC Register Fields (PMC[4,5,6,7])                  | 6-17 |

| 6-8  | Itanium <sup>™</sup> Processor Performance Monitor Overflow Register Fields (PMC[0,1,2,3]) | 6-18 |

| 6-9  | Itanium™ Processor Instruction Address Range Check Register Fields (PMC[13])               | 6-19 |

| 6-10 | Itanium <sup>™</sup> Processor Instruction Address Range Check by Instruction Set          | 6-19 |

| 6-11 | Opcode Match Register Fields (PMC[8,9])                                                    | 6-20 |

| 6-12 | Instruction Event Address Configuration Register Fields (PMC[10])                          | 6-23 |

| 6-13 | Instruction EAR (PMC[10]) umask Field in Cache Mode (PMC[10].tlb=0)                        | 6-23 |

| 6-14 | Instruction EAR (PMD[0,1]) in Cache Mode (PMC[10].tlb=0)                                   | 6-24 |

| 6-15 | Instruction EAR (PMC[10]) umask Field in TLB Mode (PMC[10].tlb=1)                          | 6-24 |

| 6-16 | Instruction EAR (PMD[0,1]) in TLB Mode (PMC[10].tlb=1)                                     | 6-24 |

| 6-17 | Data Event Address Configuration Register Fields (PMC[11])                                 | 6-25 |

| 6-18 | PMC[11] Mask Fields in Data Cache Load Miss Mode (PMC[11].tlb=0)                           | 6-26 |

| 6-19 | PMD[2,3,17] Fields in Data Cache Load Miss Mode (PMC[11].tlb=0)              | 6-26 |

|------|------------------------------------------------------------------------------|------|

| 6-20 | PMC[11] Unmask Field in TLB Miss Mode (PMC[11].tlb=1)                        |      |

| 6-21 | PMD[2,3,17] Fields in TLB Miss Mode (PMC[11].tlb=1)                          | 6-27 |

| 6-22 | IA-64 Branch Trace Buffer Configuration Register Fields (PMC[12])            | 6-28 |

| 6-23 | IA-64 Branch Trace Buffer Register Fields (PMD[8-15])                        |      |

| 6-24 | IA-64 Branch Trace Buffer Index Register Fields (PMD[16])                    |      |

| 6-25 | Information Returned by PAL_PERF_MON_INFO for the Itanium™ Processor         | 6-32 |

| 7-1  | IA-64 and IA-32 Instruction Set Execution and Retirement Monitors            |      |

| 7-2  | IA-64 and IA-32 Instruction Set Execution and Retirement Performance Metrics | 7-2  |

| 7-3  | Instruction Issue and Retirement Events                                      |      |

| 7-4  | Instruction Issue and Retirement Events (Derived)                            | 7-2  |

| 7-5  | Floating-Point Execution Monitors                                            |      |

| 7-6  | Floating-Point Execution Monitors (Derived)                                  | 7-3  |

| 7-7  | Control and Data Speculation Monitors                                        | 7-3  |

| 7-8  | Itanium™ Processor Control/Data Speculation Performance Metrics              | 7-4  |

| 7-9  | Itanium™ Processor Memory Events                                             | 7-4  |

| 7-10 | Itanium™ Processor Stall Cycle Monitors                                      | 7-4  |

| 7-11 | Itanium™ Processor Stall Cycle Monitors (Derived)                            | 7-4  |

| 7-12 | Itanium <sup>™</sup> Processor Branch Monitors                               | 7-5  |

| 7-13 | Derived Memory Hierarchy Monitors                                            | 7-6  |

| 7-14 | Itanium™ Processor Cache Performance Ratios                                  | 7-6  |

| 7-15 | L1 Instruction Cache and Instruction Prefetch Monitors                       | 7-8  |

| 7-16 | L1 Data Cache Monitors                                                       | 7-9  |

| 7-17 | L2 Cache Monitors                                                            | 7-9  |

| 7-18 | L3 Cache Monitors                                                            | 7-10 |

| 7-19 | Itanium <sup>™</sup> Processor System and TLB Monitors                       |      |

| 7-20 | Itanium <sup>™</sup> Processor System and TLB Monitors (Derived)             | 7-11 |

| 7-21 | Itanium™ Processor TLB Performance Metrics                                   |      |

| 7-22 | Slot Unit Mask for BRANCH_TAKEN_SLOT                                         |      |

| 7-23 | Retired Event Selection by Opcode Match                                      | 7-32 |

| 7-24 | Unit Mask Bits {19:16} for L2_FLUSH_DETAILS Event                            | 7-38 |

| 7-25 | Unit Mask Bits {19:18} for PIPELINE_FLUSH Event                              | 7-46 |

The IA-64 architecture is a unique combination of innovative features such as explicit parallelism, predication, speculation and more. The architecture is designed to be highly scalable to fill the ever increasing performance requirements of various server and workstation market segments. The IA-64 architecture features a revolutionary 64-bit instruction set architecture (ISA) which applies a new processor architecture technology called EPIC, or Explicitly Parallel Instruction Computing. A key feature of the IA-64 architecture is IA-32 instruction set compatibility.

The *Intel*® *IA-64 Architecture Software Developer's Manual* provides a comprehensive description of the programming environment, resources, and instruction set visible to both the application and system programmer. In addition, it also describes how programmers can take advantage of IA-64 features to help them optimize code. This manual replaces the *IA-64 Application Developer's Architecture Guide* (Document Number 245188) which contains a subset of the information presented in this four-volume set.

#### 1.1 Overview of Volume 1: IA-64 Application Architecture

This volume defines the IA-64 application architecture, including application level resources, programming environment, and the IA-32 application interface. This volume also describes optimization techniques used to generate high performance software.

#### 1.1.1 Part 1: IA-64 Application Architecture Guide

Chapter 1, "About this Manual" provides an overview of all volumes in the Intel® IA-64 Architecture Software Developer's Manual.

Chapter 2, "Introduction to the IA-64 Processor Architecture" provides an overview of the IA-64 architecture system environments.

Chapter 3, "IA-64 Execution Environment" describes the IA-64 register set used by applications and the memory organization models.

Chapter 4, "IA-64 Application Programming Model" gives an overview of the behavior of IA-64 application instructions (grouped into related functions).

Chapter 5, "IA-64 Floating-point Programming Model" describes the IA-64 floating-point architecture (including integer multiply).

Chapter 6, "IA-32 Application Execution Model in an IA-64 System Environment" describes the operation of IA-32 instructions within the IA-64 System Environment from the perspective of an application programmer.

### 1.1.2 Part 2: IA-64 Optimization Guide

Chapter 7, "About the IA-64 Optimization Guide" gives an overview of the IA-64 optimization guide.

Chapter 8, "Introduction to IA-64 Programming" provides an overview of the IA-64 application programming environment.

Chapter 9, "Memory Reference" discusses features and optimizations related to control and data speculation.

Chapter 10, "Predication, Control Flow, and Instruction Stream" describes optimization features related to predication, control flow, and branch hints.

Chapter 11, "Software Pipelining and Loop Support" provides a detailed discussion on optimizing loops through use of software pipelining.

Chapter 12, "Floating-point Applications" discusses current performance limitations in floating-point applications and IA-64 features that address these limitations.

## 1.2 Overview of Volume 2: IA-64 System Architecture

This volume defines the IA-64 system architecture, including system level resources and programming state, interrupt model, and processor firmware interface. This volume also provides a useful system programmer's guide for writing high performance system software.

### 1.2.1 Part 1: IA-64 System Architecture Guide

Chapter 1, "About this Manual" provides an overview of all volumes in the Intel® IA-64 Architecture Software Developer's Manual.

Chapter 2, "IA-64 System Environment" introduces the environment designed to support execution of IA-64 operating systems running IA-32 or IA-64 applications.

Chapter 3, "IA-64 System State and Programming Model" describes the IA-64 architectural state which is visible only to an operating system.

Chapter 4, "IA-64 Addressing and Protection" defines the resources available to the operating system for virtual to physical address translation, virtual aliasing, physical addressing, and memory ordering.

Chapter 5, "IA-64 Interruptions" describes all interruptions that can be generated by an IA-64 processor.

Chapter 6, "IA-64 Register Stack Engine" describes the IA-64 architectural mechanism which automatically saves and restores the stacked subset (GR32 – GR 127) of the general register file.

Chapter 7, "IA-64 Debugging and Performance Monitoring" is an overview of the performance monitoring and debugging resources that are available in the IA-64 architecture.

Chapter 8, "IA-64 Interruption Vector Descriptions" lists all IA-64 interruption vectors.

Chapter 9, "IA-32 Interruption Vector Descriptions" lists IA-32 exceptions, interrupts and intercepts that can occur during IA-32 instruction set execution in the IA-64 System Environment.

Chapter 10, "IA-64 Operating System Interaction Model with IA-32 Applications" defines the operation of IA-32 instructions within the IA-64 System Environment from the perspective of an IA-64 operating system.

Chapter 11, "IA-64 Processor Abstraction Layer" describes the firmware layer which abstracts IA-64 processor implementation-dependent features.

#### 1.2.2 Part 2: IA-64 System Programmer's Guide

Chapter 12, "About the IA-64 System Programmer's Guide" gives an introduction to the second section of the system architecture guide.

Chapter 13, "MP Coherence and Synchronization" describes IA-64 multi-processing synchronization primitives and the IA-64 memory ordering model.

Chapter 14, "Interruptions and Serialization" describes how the processor serializes execution around interruptions and what state is preserved and made available to low-level system code when interruptions are taken.

Chapter 15, "Context Management" describes how operating systems need to preserve IA-64 register contents and state. This chapter also describes IA-64 system architecture mechanisms that allow an operating system to reduce the number of registers that need to be spilled/filled on interruptions, system calls, and context switches.

Chapter 16, "Memory Management" introduces various IA-64 memory management strategies.

Chapter 17, "Runtime Support for Control and Data Speculation" describes the operating system support that is required for control and data speculation.

Chapter 18, "Instruction Emulation and Other Fault Handlers" describes a variety of instruction emulation handlers that IA-64 operating system are expected to support.

Chapter 19, "Floating-point System Software" discusses how IA-64 processors handle floating-point numeric exceptions and how the IA-64 software stack provides complete IEEE-754 compliance.

Chapter 20, "IA-32 Application Support" describes the support an IA-64 operating system needs to provide to host IA-32 applications.

Chapter 21, "External Interrupt Architecture" describes the IA-64 external interrupt architecture with a focus on how external asynchronous interrupt handling can be controlled by software.

Chapter 22, "I/O Architecture" describes the IA-64 I/O architecture with a focus on platform issues and support for the existing IA-32 I/O port space platform infrastructure.

Chapter 23, "Performance Monitoring Support" describes the IA-64 performance monitor architecture with a focus on what kind of operating system support is needed from IA-64 operating systems.

Chapter 24, "Firmware Overview" introduces the IA-64 firmware model, and how various firmware layers (PAL, SAL, EFI) work together to enable processor and system initialization, and operating system boot.

#### 1.2.3 Appendices

Appendix A, "IA-64 Resource and Dependency Semantics" summarizes the dependency rules that are applicable when generating code for IA-64 processors.

Appendix B, "Code Examples" provides OS boot flow sample code.

### 1.3 **Overview of Volume 3: Instruction Set Reference**

This volume is a comprehensive reference to the IA-64 and IA-32 instruction sets, including instruction format/encoding.

#### 1.3.1 Part 1: IA-64 Instruction Set Descriptions

Chapter 1, "About this Manual" provides an overview of all volumes in the Intel® IA-64 Architecture Software Developer's Manual.

Chapter 2, "IA-64 Instruction Reference" provides a detailed description of all IA-64 instructions, organized in alphabetical order by assembly language mnemonic.

Chapter 3, "IA-64 Pseudo-Code Functions" provides a table of pseudo-code functions which are used to define the behavior of the IA-64 instructions.

Chapter 4, "IA-64 Instruction Formats" describes the encoding and instruction format instructions.

#### 1.3.2 Part 2: IA-32 Instruction Set Descriptions

Chapter 5, "Base IA-32 Instruction Reference" provides a detailed description of all base IA-32 instructions, organized in alphabetical order by assembly language mnemonic.

Chapter 6, "IA-32 MMX<sup>TM</sup> Technology Instruction Reference" provides a detailed description of all IA-32 MMX<sup>TM</sup> technology instructions designed to increase performance of multimedia intensive applications. Organized in alphabetical order by assembly language mnemonic.

Chapter 7, "IA-32 Streaming SIMD Extension Instruction Reference" provides a detailed description of all IA-32 Streaming SIMD Extension instructions designed to increase performance of multimedia intensive applications, and is organized in alphabetical order by assembly language mnemonic.

# 1.4 Overview of Volume 4: *Itanium*<sup>™</sup> *Processor Programmer's Guide*

This volume describes model-specific architectural features incorporated into the Intel® Itanium<sup>TM</sup> processor, the first IA-64 processor.

Chapter 1, "About this Manual" provides an overview of four volumes in the Intel® IA-64 Architecture Software Developer's Manual.

Chapter 2, "Register Stack Engine Support" summarizes Register Stack Engine (RSE) support provided by the Itanium processor.

Chapter 3, "Virtual Memory Management Support" details size of physical and virtual address, region register ID, and protection key register implemented on the Itanium processor.

Chapter 4, "Processor Specific Write Coalescing (WC) Behavior" describes the behavior of write coalesce (also known as Write Combine) on the Itanium processor.

Chapter 5, "Model Specific Instruction Implementation" describes model specific behavior of IA-64 instructions on the Itanium processor.

Chapter 6, "Processor Performance Monitoring" defines the performance monitoring features which are specific to the Itanium processor. This chapter outlines the targeted performance monitor usage models and describes the Itanium processor specific performance monitoring state.

Chapter 7, "Performance Monitor Events" summarizes the Itanium processor events and describes how to compute commonly used performance metrics for Itanium processor events.

Chapter 8, "Model Specific Behavior for IA-32 Instruction Execution" describes some of the key differences between an Itanium processor executing IA-32 instructions and the Pentium® III processor.

### 1.5 Terminology

The following definitions are for terms related to the IA-64 architecture and will be used throughout this document:

**Instruction Set Architecture (ISA)** – Defines application and system level resources. These resources include instructions and registers.

**IA-64** Architecture – The new ISA with 64-bit instruction capabilities, new performanceenhancing features, and support for the IA-32 instruction set.

**IA-32** Architecture – The 32-bit and 16-bit Intel Architecture as described in the *Intel Architecture Software Developer's Manual.*

**IA-64 Processor** – An Intel 64-bit processor that implements both the IA-64 and the IA-32 instruction sets.

**IA-64 System Environment** – The IA-64 operating system privileged environment that supports the execution of both IA-64 and IA-32 code.

**IA-32 System Environment** – The operating system privileged environment and resources as defined by the *Intel Architecture Software Developer's Manual*. Resources include virtual paging, control registers, debugging, performance monitoring, machine checks, and the set of privileged instructions.

IA-64 Firmware – The Processor Abstraction Layer (PAL) and System Abstraction Layer (SAL).

**Processor Abstraction Layer (PAL)** – The IA-64 firmware layer which abstracts IA-64 processor features that are implementation dependent.

**System Abstraction Layer (SAL)** – The IA-64 firmware layer which abstracts IA-64 system features that are implementation dependent.

### 1.6 Related Documents

The following documents contain additional material related to the *Intel*® *IA-64 Architecture Software Developer's Manual*:

- *Intel Architecture Software Developer's Manual* This set of manuals describes the Intel 32-bit architecture. They are readily available from the Intel Literature Department by calling 1-800-548-4725 and requesting Document Numbers 243190, 243191and 243192, or can be downloaded at http://developer.intel.com/design/litcentr.

- *IA-64 Software Conventions and Runtime Architecture Guide* This document (Document Number 245358) defines general information necessary to compile, link, and execute a program on an IA-64 operating system. It can be downloaded at http://developer.intel.com/design/ia64.

- *IA-64 System Abstraction Layer Specification* This document (Document Number 245359) specifies requirements to develop platform firmware for IA-64 processor systems.

- *Extensible Firmware Interface Specification* This document defines a new model for the interface between operating systems and platform firmware. It can be downloaded at http://developer.intel.com/technology/efi.

### 1.7 Revision History

| Date of<br>Revision | Revision<br>Number | Description                                                           |  |

|---------------------|--------------------|-----------------------------------------------------------------------|--|

| July 2000           | 1.1                | /olume 1:                                                             |  |

|                     |                    | Processor Serial Number feature removed (Chapter 3)                   |  |

|                     |                    | Clarification on exceptions to instruction dependency (Section 3.4.3) |  |

| Date of<br>Revision | Revision<br>Number | Description                                                                                                                                                                                           |  |

|---------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     |                    | Volume 2:                                                                                                                                                                                             |  |

|                     |                    | Clarifications regarding "reserved" fields in ITIR (Chapter 3)                                                                                                                                        |  |

|                     |                    | Instruction and Data translation must be enabled for executing IA-32 instructions (Chapters 3,4 and 10)                                                                                               |  |

|                     |                    | FCR/FDR mappings, and clarification to the value of PSR.ri after an RFI (Chapters 3 and 4)                                                                                                            |  |

|                     |                    | Clarification regarding ordering data dependency                                                                                                                                                      |  |

|                     |                    | Out-of-order IPI delivery is now allowed (Chapters 4 and 5)                                                                                                                                           |  |

|                     |                    | Content of EFLAG field changed in IIM (p. 9-24)                                                                                                                                                       |  |

|                     |                    | PAL_CHECK and PAL_INIT calls – exit state changes (Chapter 11)                                                                                                                                        |  |

|                     |                    | PAL_CHECK processor state parameter changes (Chapter 11)                                                                                                                                              |  |

|                     |                    | PAL_BUS_GET/SET_FEATURES calls – added two new bits (Chapter 11)                                                                                                                                      |  |

|                     |                    | PAL_MC_ERROR_INFO call – Changes made to enhance and simplify the call to provide more information regarding machine check (Chapter 11)                                                               |  |

|                     |                    | PAL_ENTER_IA_32_Env call changes – entry parameter represents the entry order; SAL needs to initialize all the IA-32 registers properly before making this call (Chapter 11)                          |  |

|                     |                    | PAL_CACHE_FLUSH – added a new cache_type argument (Chapter 11)                                                                                                                                        |  |

|                     |                    | PAL_SHUTDOWN – removed from list of PAL calls (Chapter 11)                                                                                                                                            |  |

|                     |                    | Clarified memory ordering changes (Chapter 13)                                                                                                                                                        |  |

|                     |                    | Clarification in dependence violation table (Appendix A)                                                                                                                                              |  |

|                     |                    | Volume 3:                                                                                                                                                                                             |  |

|                     |                    | fmix instruction page figures corrected (Chapter 2)                                                                                                                                                   |  |

|                     |                    | Clarification of "reserved" fields in ITIR (Chapters 2 and 3)                                                                                                                                         |  |

|                     |                    | Modified conditions for alloc/loadrs/flushrs instruction placement in bundle/<br>instruction group (Chapters 2 and 4)                                                                                 |  |

|                     |                    | IA-32 JMPE instruction page typo fix (p. 5-238)                                                                                                                                                       |  |

|                     |                    | Processor Serial Number feature removed (Chapter 5)                                                                                                                                                   |  |

|                     |                    | Volume 4:                                                                                                                                                                                             |  |

|                     |                    | Reformatted the Performance Monitor Events chapter for readability and ease of use (no changes to any of the events except for renaming of some); events are listed in alphabetical order (Chapter 7) |  |

| January 2000        | 1.0                | Initial release of document.                                                                                                                                                                          |  |

# **Register Stack Engine Support**

### 2.1 RSE Modes

The Itanium processor implements the enforced lazy RSE mode. Refer to Chapter 6, "IA-64 Register Stack Engine" in Volume 2 for a description of the RSE modes.

### 2.2 RSE and Clean Register Stack Partitions

On the Itanium processor, the internal RSE pointer RSE.BSPLoad is always equal to AR.BSPStore, meaning that the size of the clean register stack partition is always zero. This implies that, on the Itanium processor, a flushrs instruction will create a dirty region of size zero and an invalid region of size equal to 96 - CFM.sof. On other implementations that maintain a clean partition, flushrs behavior may differ by creating a clean register stack partition in addition to an invalid partition and a zero-sized dirty partition. As a result, the Itanium processor's RSE may perform more mandatory fills upon a branch-return (br.ret) or rfi following a flushrs instruction than an implementation that maintains a clean partition.

# Virtual Memory Management Support 3

### 3.1 Page Size Supported

The following page sizes are supported on the Itanium processor: 4K, 8K, 16K, 64K, 256K, 1M, 4M, 16M and 256M bytes.

#### 3.2 Physical and Virtual Addresses

The IA-64 architecture requires that a processor implement at least 54 virtual address bits and 32 physical address bits. The Itanium processor implements 54 virtual address bits (51 address bits plus 3 region index bits) and 44 physical address bits.

### 3.3 Region Register ID

The Itanium processor implements the minimum region register IDs allowed by the IA-64 architecture. The region register ID contains 18 bits.

### 3.4 Protection Key Register

The IA-64 architecture requires a minimum of 16 protection key registers, each at least as wide as the region register IDs. The Itanium processor implements 16 protection key registers, each 21 bits wide.

# **Processor Specific Write Coalescing** (WC) Behavior

## 4.1 Write Coalescing

For increased performance of uncacheable references to frame buffers, previous Intel IA-32 processors defined the Write Coalescing (WC) memory type. WC coalesces streams of data writes into a single larger bus write transaction. Refer to the *Intel Architecture Software Developer's Manual* for additional information.

On the Itanium processor, WC loads are performed directly from memory and not from coalescing buffers. It has a separate 2-entry, 64-byte Write Coalesce Buffer (WCB) which is used exclusively for WC accesses. Each byte in the line has a valid bit. If all the valid bits are true, then the line is full and will be evicted (or flushed) by the processor.

**Note:** WC behavior of the Itanium processor in the IA-32 System Environment is similar to the Pentium III processor. Refer to the *Intel Architecture Software Developer's Manual* for more information.

### 4.2 WC Buffer Eviction Conditions

To ensure consistency with memory, the WCB is flushed on the following conditions (both entries are flushed). These conditions are followed when the processor is operating in the IA-64 System Environment:

#### Table 4-1. Itanium<sup>™</sup> Processor WCB Eviction Conditions

| Eviction Condition                     | IA-64 Instructions                       |

|----------------------------------------|------------------------------------------|

| Memory Fence (mf)                      | mf                                       |

| Architectural Conditions for WCB Flush |                                          |

| Memory Release ordering (op.rel)       | st.rel, cmpxchg.rel, fetchadd.rel, ptc.g |

| Flush Cache (fc) hit on WCB            | yes                                      |

| Flush Write Buffers (fwb)              | yes                                      |

| Any UC load                            | no <sup>a</sup>                          |

| Any UC store                           | no <sup>a</sup>                          |

| UC load or ifetch hits WCB             | no <sup>a</sup>                          |

| UC store hits WCB                      | no <sup>a</sup>                          |

| WC load/ifetch hits WCB                |                                          |

| WC store hits WCB                      |                                          |

a. IA-64 architecture doesn't require the WC buffers to be coherent w.r.t to UC load/store operations.

### 4.3 WC Buffer Flushing Behavior

As mentioned previously, the Itanium processor WCB contains two entries. The WC entries are flushed in the same order as they are allocated. That is, the entries are flushed in written order. This flushing order applies only to a "well-behaved" stream. A "well-behaved" stream writes one WC entry at a time and does not write the second WC entry until the first one is full.

In the absence of platform retry or deferral, the flushing rule implies that the WCB entries are always flushed in a program written order for a "well-behaved" stream, even in the presence of interrupts. For example, consider the following scenario: if software issues a "well-behaved" stream, but is interrupted in the middle; one of the WC entries could be partially filled. The WCB (including the partially filled entry) could be flushed by the OS kernel code or by other processes. When the interrupted context resumes, it sends out the remaining line and then moves on to fill the other entry. Note that the resumed context could be interrupted again in the middle of filling up the other entry, causing both entries to be partially filled when the interrupt occurs.

For streams that do not conform to the above "well-behaved" rule, the order in which the WC buffer is flushed is random.

WCB eviction is performed for full lines by a single 64-byte bus transaction in a stream of 8-byte packages. For partially full lines, the WCB is evicted using up to eight 8-byte transactions with the proper byte enables. When flushing, WC transactions are given the highest priority of all external bus operations.

# Model Specific Instruction Implementation

This section describes how IA-64 instructions with processor implementation-specific features, behave on the Intel Itanium processor.

### 5.1 Id.bias

If the instruction hits  $L1D^1$  or L2 cache and the state of the line is exclusive (E) or modified (M), the line is returned and remains in cache; no external bus traffic is generated. If the line is shared (S) or invalid (I) or the instruction misses the L2, it is treated as a store miss by the L3/bus. The line is returned and stored in E state by the processor in the L2 and L3 cache.

Please refer to page 2-124 in Volume 3 for a detailed description of the 1d instruction.

#### 5.2 Ifetch Exclusive Hint

The exclusive hint in the lfetch instruction allows the cache line to be fetched in an exclusive (E) state. On the Itanium processor, an lfetch transaction that has a snoop hit will be cached in an shared (S) state; otherwise, it is cached in an exclusive state.

Please refer to page 2-135 in Volume 3 for a detailed description of the lfetch instruction.

#### 5.3 fwb

The Itanium processor implements the flush write-back buffer (fwb) instruction. This instruction carries a weak memory attribute and causes the coalescing buffer to be flushed. The L1D and L2 store buffers are not flushed.

Please refer to page 2-115 in Volume 3 for a detailed description of the fwb instruction.

<sup>1.</sup> The Intel® Itanium<sup>™</sup> processor cache hierarchy consists of the following levels: on-chip L1I, L1D, L2 caches, and off-chip L3 cache.

#### 5.4 thash

The IA-64 architecture defines a thash instruction for generating the hash address for long format VHPT. thash is implementation specific. On the Itanium processor, since the hashing function is performed in the HPW, the HPW will generate the VHPT Entry which corresponds to the virtual address supplied. The hashing function is given in the following pseudo-code:

```

If (GR[r3].nat = '1 or unimplemented virtual address bits) then {

GR[r1] = '0 ;

// treated as a speculative access.

GR[r1].nat = '1;

}

else {

Mask = (2^PTA.size) - 1;

HPN = VA{50:0} >> RR[VA{63:61}].ps; // Hash Page Number unsigned right shift.

// mov 2 RR checks for supported ps

if (PTA.vf=32) {

// 32B PTE (Long format)

Hash_Index = HPN ^ (zero{63:18} || rid{17:0})

VHPT_Offset = Hash_Index << 5 ;</pre>

}

if (PTA.vf=8) {

// 8B PTE

Hash_Index = HPN ;

VHPT_Offset = Hash_Index << 3;</pre>

}

GR[r1] = (PTA.base{63:61} << 61)

|| ([(PTA.base{60:15} & ~Mask{60:15}) ||

(VHPT_Offset{60:15} & Mask{60:15})] << 15)

|| VHPT_Offset{14:0} ;

}

}

```

Please refer to page 2-223 in Volume 3 for a detailed description of the thash instruction.

### 5.5 ttag

The IA-64 architecture defines the ttag instruction for generating the tag for a long format VHPT entry. ttag is implementation specific. The HPW will generate the tag for the long format VHPT entry which corresponds to the virtual address supplied. The function is:

Please refer to page 2-227 in Volume 3 for a detailed description of the ttag instruction.

### 5.6 ptc.e

On the Itanium processor, a single ptc.e purges all translation cache (TC) entries in both the instruction and data TLBs. The caches are not flushed.

Please refer to page 2-191 in Volume 3 for a detailed description of the ptc instruction.

### 5.7 mf.a

In the IA-64 architecture, the mf.a instruction is a memory acceptance fence for UC transactions only. On the Itanium processor, mf.a is implemented as an acceptance fence for both cacheable and UC data transactions (but not I fetches). The processor stalls until all data buffers in the L2 and bus are empty. This does not include buffers for instruction and L3 WB buffer in the bus request queue.

Please refer to page 2-138 in Volume 3 for a detailed description of the mf instruction.

### 5.8 Prefetch Behavior

The Itanium processor does not initiate prefetches with post-increment loads.

### 5.9 Temporal and Non-temporal Hints Support

IA-64 architecture provides memory locality hints for data accesses that can be used for allocation control in the processor cache hierarchy. For more details on this topic, please refer to Volume 1, Section 4.4.6. Implementation of locality hints is left as an implementation-specific feature on IA-64 processors.

On the Itanium processor, four types of memory locality hints are implemented: t1, nt1, nt2 and nta. The Itanium processor does not support a non-temporal buffer; instead, non-temporal accesses are allocated in L2 cache with biased replacement.

# **Processor Performance Monitoring** 6

This chapter defines the performance monitoring features on the Itanium processor. The Itanium processor provides four 32-bit performance counters, more than 50 monitorable events, and several advanced monitoring capabilities. This chapter outlines the targeted performance monitor usage models, defines the software interface and programming model, and lists the set of monitored events.

IA-64 architecture incorporates architected mechanisms that allow software to actively and directly manage performance critical processor resources such as branch prediction structures, processor data and instruction caches, virtual memory translation structures, and more. To achieve the highest performance levels, dynamic processor behavior can be monitored and fed back into the code generation process to improve observed run-time behavior or to expose higher levels of instruction level parallelism. One can quantify and measure behavior of real-world IA-64 applications, tools and operating systems. These measurements will be critical for compiler optimizations and the efficient use of several architectural features such as speculation, predication, and more.

The remainder of this chapter is split into the following two subsections:

- Section 6.1, "Performance Monitor Programming Models" discusses how performance monitors are used and presents various Itanium processor performance monitoring programming models.

- Section 6.2, "Performance Monitor State" defines the Itanium processor specific PMC/PMD performance monitoring registers.

#### 6.1 **Performance Monitor Programming Models**

This section introduces the Itanium processor performance monitoring features from a programming model point-of-view and describes how the different event monitoring mechanisms can be used effectively. The Itanium processor performance monitor architecture focuses on the following two usage models:

- Workload Characterization: the first step in any performance analysis is to understand the performance characteristics of the workload under study. Section 6.1.1, "Workload Characterization" discusses the Itanium processor support for workload characterization.

- **Profiling**: profiling is used by application developers and profile-guided compilers. Application developers are interested in identifying performance bottlenecks and relating them back to their code. Their primary objective is to understand which program location caused performance degradation at the module, function, and basic block level. For optimization of data placement and the analysis of critical loops, instruction level granularity is desirable. Profile-guided compilers that use advanced IA-64 architectural features such as predication and speculation benefit from run-time profile information to optimize instruction schedules. The Itanium processor supports instruction granular statistical profiling of branch mispredicts and cache misses. Details of the Itanium processor's profiling support are described in Section 6.1.2, "Profiling".

Whenever monitoring overhead is irrelevant, but accuracy is the primary objective, system and processor designers may resort to tracing processor activity at the system or the processor bus interface. However, trace based performance analysis and hardware tracing of the Itanium processor are beyond the scope of this documentation.

#### 6.1.1 Workload Characterization

The first step in any performance analysis is to understand the performance characteristics of the workload under study. There are two fundamental measures of interest: event rates and program cycle break down.

- Event Rate Monitoring: Event rates of interest include average retired instructions-per-clock (IPC), data and instruction cache miss rates, or branch mispredict rates measured across the entire application. Characterization of operating systems or large commercial workloads (e.g. OLTP analysis) requires a system-level view of performance relevant events such as TLB miss rates, VHPT walks/second, interrupts/second or bus utilization rates. Section 6.1.1.1, "Event Rate Monitoring" discusses event rate monitoring.

- Cycle Accounting: The cycle break-down of a workload attributes a reason to every cycle spent by a program. Apart from a program's inherent execution latency, extra cycles are usually due to pipeline stalls and flushes. Section 6.1.1.4, "Cycle Accounting" discusses cycle accounting.

#### 6.1.1.1 Event Rate Monitoring

Event rate monitoring determines event rates by reading processor event occurrence counters before and after the workload is run and then computing the desired rates. For instance, two basic Itanium processor events that count the number of retired IA-64 instructions (IA64\_INST\_RETIRED.u) and the number of elapsed clock cycles (CPU\_CYCLES) allow a workload's instructions per cycle (IPC) to be computed as follows:

$IPC = (IA64\_INST\_RETIRED.u_{t1} - IA64\_INST\_RETIRED.u_{t0}) / (CPU\_CYCLES_{t1} - CPU\_CYCLES_{t0})$

Time-based sampling is the basis for many performance debugging tools [VTune, gprof, Windows NT\*]. As shown in Figure 6-1, time-based sampling can be used to plot the event rates over time, and can provide insights into the different phases the workload moves through.

On the Itanium processor, many event types (e.g. TLB misses or branch mispredicts) are limited to a rate of one per clock cycle. These are referred to as "single occurrence" events. However, in the Itanium processor multiple events of the same type may occur in the same clock. We refer to such events as "multi-occurrence" events. An example of a multi-occurrence events on the Itanium processor is data cache misses (up to two per clock). Multi-occurrence events, such as the number of entries in the memory request queue, can be used to the derive average number and average latency of memory accesses. The next two sections describe the basic Itanium processor mechanisms for monitoring single and multi-occurrence events.

#### 6.1.1.2 Single Occurrence Events and Duration Counts

A single occurrence event can be monitored by any of the Itanium processor performance counters. For all single occurrence events a counter is incremented by up to one per clock cycle. Duration counters that count the number of clock cycles during which a condition persists are considered "single occurrence" events. Examples of single occurrence events on the Itanium processor are TLB misses, branch mispredictions, or cycle-based metrics.

#### 6.1.1.3 Multi-occurrence Events, Thresholding and Averaging

Events that, due to hardware parallelism, may occur at rates greater than one per clock cycle are termed "multi-occurrence" events. Examples of such events on the Itanium processor are retired instructions or the number of live entries in the memory request queue. The Itanium processor's four performance counters are asymmetrical. While all counters handle single-occurrence and multi-occurrence events with event rates up to three per cycle, only two counters can handle multi-occurrence events with event rates up to seven per cycle. For details, see Section 6.2.2, "Performance Counter Registers".

Thresholding capabilities are available in the Itanium processor's multi-occurrence counters and can be used to plot an event distribution histogram. When a non-zero threshold is specified, the monitor is incremented by one in every cycle in which the observed event count exceeds that programmed threshold. This allows questions such as "for how many cycles did the memory request queue contain more than two entries?" or "during how many cycles did the machine retire more than three instructions?" to be answered. This capability allows micro-architectural buffer sizing experiments to be supported by real measurements. By running a benchmark with different threshold values, a histogram can be drawn up that may help to identify the performance "knee" at a certain buffer size.

For overlapping concurrent events, such as pending memory operations, the average number of concurrently outstanding requests and the average number of cycles that requests were pending is of interest. To calculate the average number or latency of multiple outstanding requests in the memory queue, we need to know the total number of requests ( $n_{total}$ ) and, in each cycle, the number of live requests per cycle ( $n_{live}/cycle$ ). By summing up the live requests ( $n_{live}/cycle$ ) using a multi-occurrence counter  $\Sigma$ nlive is directly measured by hardware. We can now calculate the average number of requests and the average latency as follows:

- Average outstanding requests/cycle =  $\Sigma n_{live} / \Delta t$

- Average latency per request =  $\Sigma n_{live} / n_{total}$

An example of this calculation is given in Table 6-1, in which the average outstanding requests/cycle = 15/8 = 1.825, and the average latency per request = 15/5 = 3 cycles.

| Time [Cycles]      | 1 | 2 | 3 | 4 | 5  | 6  | 7  | 8  |

|--------------------|---|---|---|---|----|----|----|----|

| # Requests In      | 1 | 1 | 1 | 1 | 1  | 0  | 0  | 0  |

| # Requests Out     | 0 | 0 | 0 | 1 | 1  | 1  | 1  | 1  |

| n <sub>live</sub>  | 1 | 2 | 3 | 3 | 3  | 2  | 1  | 0  |

| $\Sigma n_{live}$  | 1 | 3 | 6 | 9 | 12 | 14 | 15 | 15 |

| n <sub>total</sub> | 1 | 2 | 3 | 4 | 5  | 5  | 5  | 5  |

#### Table 6-1. Average Latency per Request and Requests per Cycle Calculation Example

The Itanium processor provides the following capabilities to support event rate monitoring:

- Clock cycle counter

- Retired instruction counter

- · Event occurrence and duration counters

- Multi-occurrence counters with thresholding capability

#### 6.1.1.4 Cycle Accounting

While event rate monitoring counts the number of events, it does not tell us whether the observed events are contributing to a performance problem. A commonly used strategy is to plot multiple event rates and correlate them with the measured instructions per cycle (IPC) rate. If a low IPC occurs concurrently with a peak of cache miss activity, chances are that cache misses are causing a performance problem. To eliminate such guess work, the Itanium processor provides a set of IA-64 cycle accounting monitors, that break-down the number of cycles that are lost due to various kinds of micro-architectural events. As shown in Figure 6-2, this lets us account for every cycle spent by a program and therefore provides insight into an application's micro-architectural behavior. Note that cycle accounting is different from simple stall or flush duration counting. Cycle accounting is based on the machine's actual stall and flush conditions and accounts for overlapped pipeline delays, while simple stall or flush duration counters do not. Cycle accounting determines a program's cycle break-down by stall and flush reasons, while simple duration counters are useful in determining cumulative stall or flush latencies.

#### Figure 6-2. IA-64 Cycle Accounting

The Itanium processor cycle accounting monitors account for all major single and multi-cycle stall and flush conditions. Overlapping stall and flush conditions are prioritized in reverse pipeline order (i.e. delays that occur later in the pipe and that overlap with earlier stage delays are reported as being caused later in the pipeline). The eight stall and flush reasons are prioritized in the following order:

- 1. Branch Mispredict Cycle: branch mispredicts, pipeline flushes (includes interrupts and exceptions)

- 2. Data Access Cycle: memory pipeline full, data TLB stalls, and load-use stalls

- 3. Execution Latency Cycle: scoreboard stalls and FPU stalls

- 4. RSE Active Cycle: RSE spill/fill stall

- 5. Issue Limit Cycle: instruction issue, stops, or resource oversubscription stalls

- 6. Instruction Access Cycle: instruction fetch stalls due to instruction cache or TLB misses

- 7. Taken Branch Cycle: instruction fetch branch bubbles

- Fetch Window Cycle: partial instruction fetch stalls due to non instruction cache line aligned branch targets

Four of the eight categories (1,2,3,6) are directly measurable as the Itanium processor events. The other four categories (4,5,7,8) are not measured directly. Instead four combined categories are available as the Itanium processor events: branch cycles (1+7), memory cycles (2+4), execution cycles (3+5), and instruction fetch cycles (6+8) are directly measurable as a Itanium processor event. For details refer to Section 7.4, "Cycle Accounting Events" on page 7-4.

#### 6.1.2 Profiling

Profiling is used by application developers and profile-guided compilers, optimizing linkers and run-time systems. Application developers are interested in identifying performance bottlenecks and relating them back to their source code. Based on profile feedback developers can make changes to the high-level algorithms and data structures of the program. Compilers can use profile feedback to optimize instruction schedules by employing advanced IA-64 architectural features such as predication and speculation.

To support profiling, performance monitor counts have to be associated with program locations. The following mechanisms are supported directly by the Itanium processor's performance monitors:

- Program Counter Sampling

- Miss Event Address Sampling: Itanium processor Event Address Registers (EARs) provide sub-pipeline length event resolution for performance critical events (instruction and data caches, branch mispredicts, instruction and data TLBs).

- Event Qualification: constrains event monitoring to a specific instruction address range, to certain opcodes or privilege levels.

These profiling features are presented in the next three subsections.

#### 6.1.2.1 Program Counter Sampling

Application tuning tools like [VTune, gprof] use time-based or event-based sampling of the program counter and other event counters to identify performance critical functions and basic blocks. As shown in Figure 6-3, the sampled points can be histogrammed by instruction addresses. For application tuning, statistical sampling techniques have been very successful, because the programmer can rapidly identify code hot-spots in which the program spends a significant fraction of its time or where certain event counts are high.

#### Figure 6-3. Event Histogram by Program Counter

Program counter sampling points the performance analysts at code hot-spots, but does not indicate what caused the performance problem. Inspection and manual analysis of the hot-spot region along with a fair amount of guess work are required to identify the root cause of the performance problem. On the Itanium processor, the cycle accounting mechanism (described in Section 6.1.1.4, "Cycle Accounting") can be used to directly measure an application's micro-architectural behavior.

The IA-64 architectural interval timer facilities (ITC and ITM registers) can be used for time-based program counter sampling. Event-based program counter sampling is supported by a dedicated performance monitor overflow interrupt mechanism described in detail in Volume 2, Section 7.2.2, "Performance Monitor Overflow Status Registers (PMC[0]..PMC[3])".

To support program counter sampling, the Itanium processor provides the following mechanisms:

- Timer interrupt for time-based program counter sampling.

- Event count overflow interrupt for event-based program counter sampling.

- Hardware supported cycle accounting.

#### 6.1.2.2 Miss Event Address Sampling

Program counter sampling and cycle accounting provide an accurate picture of cumulative micro-architectural behavior, but they do not provide the application developer with pointers to specific program elements (code locations and data structures) that repeatedly cause micro-architectural "miss events". In a cache study of the SPEC92 benchmarks, [Lebeck] used (trace based) cache miss profiling to gain performance improvements of 1.02 to 3.46 on various benchmarks by making simple changes to the source code. This type of analysis requires identification of instruction and data addresses related to micro-architectural "miss events" such as cache misses, branch mispredicts, or TLB misses. Using symbol tables or compiler annotations these addresses can be mapped back to critical source code elements. Like Lebeck, most performance analysts in the past have had to capture hardware traces and resort to trace driven simulation.

Due to the super-scalar issue, deep pipelining, and out-of-order instruction completion of today's micro-architectures, the sampled program counter value may not be related to the instruction address that caused a miss event. On a Pentium processor pipeline, the sampled program counter may be off by 2 dynamic instructions from the instruction that caused the miss event. On a Pentium Pro processor, this distance increases to approximately 32 dynamic instructions. On the Itanium processor it is approximately 48 dynamic instructions. If program counter sampling is used for miss event address identification on the Itanium processor, a miss event might be associated with an instruction almost five dynamic basic blocks away from where it actually occurred (assuming that 10% of all instructions are branches). Therefore, it is essential for hardware to precisely identify an event's address.

The Itanium processor provides a set of *event address registers* (EARs) that record the instruction and data addresses of data cache misses for loads, the instruction and data addresses of data TLB misses, the instruction addresses of instruction TLB and cache misses. A four deep *branch trace buffer* captures sequences of branch instructions. Table 6-2 summarizes the capabilities offered by the EARs and branch trace buffer. Exposing miss event addresses to software allows them to be monitored either by sampling or by code instrumentation. This eliminates the need for trace generation to identify and solve performance problems and enables performance analysis by a much larger audience on unmodified hardware.

| Event Address Register    | Triggers on                                                                        | What is Recorded                                                                                |

|---------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Instruction Cache         | Instruction fetches that miss<br>the L1 instruction cache<br>(demand fetches only) | Instruction Address<br>Number of cycles fetch was in flight                                     |

| Instruction TLB (ITLB)    | Instruction fetch missed ITLB (demand fetches only)                                | Instruction Address<br>Who serviced TLB miss: VHPT or software                                  |

| Data Cache                | Load instructions that miss L1 data cache                                          | Instruction Address<br>Data Address<br>Number of cycles load was in flight.                     |

| Data TLB<br>(DTLB)        | Data references that miss<br>L1 DTLB                                               | Instruction Address<br>Data Address<br>Who serviced TLB miss: L2 DTLB, VHPT or<br>software      |

| Branch<br>Trace<br>Buffer | Branch Outcomes                                                                    | Branch Instruction Address<br>Branch Target Instruction Address<br>Mispredict status and reason |

#### Table 6-2. Itanium<sup>™</sup> Processor EARs and Branch Trace Buffer

The Itanium processor EARs enable statistical sampling by configuring a performance counter to count, for instance, the number of data cache misses or retired instructions. The performance counter value is set up to interrupt the processor after a pre-determined number of events have been observed. The data cache event address register repeatedly captures the instruction and data addresses of actual data cache load misses. Whenever the counter overflows, miss event address collection is suspended until the event address register is read by software (this prevents software from capturing a miss event that might be caused by the monitoring software itself). When the counter overflows an interrupt is delivered to software, the observed event addresses are collected, and a new observation interval can be setup by rewriting the performance counter register. For time-based (rather than event-based) sampling methods, the event address registers indicate to software whether or not a qualified event was captured. Statistical sampling can achieve arbitrary event resolution by varying the number of events within an observation interval, and by increasing the number of observation intervals.

#### 6.1.3 Event Qualification

On the Itanium processor, performance monitoring can be confined to a subset of all events. As shown in Figure 6-4, events can be qualified for monitoring based on an instruction address range, a particular instruction opcode, a data address range, an event specific "unit-mask", the privilege level and instruction set the event was caused by, and the status of the performance monitoring freeze bit (PMC[0].fr).

- IA-64 Instruction Address Range Check: The Itanium processor allows event monitoring to be constrained to a programmable instruction address range. This enables monitoring of dynamically linked libraries (DLL), functions, or loops of interest in the context of a large IA-64 application. The IA-64 instruction address range check is applied at the instruction fetch stage of the pipeline and the resulting qualification is carried by the instruction throughout the pipeline. This enables conditional event counting at a level of granularity smaller than dynamic instruction length of the pipeline (approximately 48 instructions). The Itanium processor's instruction address range check operates only during IA-64 code execution (i.e. when PSR.is is zero). For details, see Section 6.2.4, "IA-64 Instruction Address Range Check Register (PMC[13])".

- IA-64 Instruction Opcode Match: The Itanium processor provides two independent IA-64 opcode match registers each of which match the currently issued instruction encodings with a programmable opcode match and mask function. The resulting match events can be selected as an event type for counting by the performance counters. This allows histogramming of instruction types, usage of destination and predicate registers as well as basic block profiling (through insertion of tagged nops). The opcode matcher operates only during IA-64 code execution (i.e. when PSR.is is zero). Details are described in Section 6.2.5, "IA-64 Opcode Match Registers (PMC[8,9])".

- IA-64 Data Address Range Check: The Itanium processor allows event collection for memory operations to be constrained to a programmable data address range. This enables selective monitoring of data cache miss behavior of specific data structures. For details, see Section 6.2.6, "IA-64 Data Address Range Check (PMC[11])".

- Event Specific Unit Masks: Some events allow the specification of "unit masks" to filter out interesting events directly at the monitored unit. For details, refer to the event pages in Chapter 7, "Performance Monitor Events".

- Privilege Level: Two bits in the processor status register are provided to enable selective process-based event monitoring. The Itanium processor supports conditional event counting based on the current privilege level; this allows performance monitoring software to break-down event counts into user and operating system contributions. For details on how to constrain monitoring by privilege level refer to Section 6.2.1, "Performance Monitor Control and Accessibility".

- Instruction Set: The Itanium processor supports conditional event counting based on the currently executing instruction set (IA-64 or IA-32) by providing two instruction set mask bits for each event monitor. This allows performance monitoring software to break-down event counts into IA-64 and IA-32 contributions. For details, refer to Section 6.2.1, "Performance Monitor Control and Accessibility".

- Performance Monitor Freeze: Event counter overflows or software can freeze event monitoring. When frozen, no event monitoring takes place until software clears the monitoring freeze bit (PMC[0].fr). This ensures that the performance monitoring routines themselves, e.g. counter overflow interrupt handlers or performance monitoring context switch routines, do not "pollute" the event counts of the system under observation.

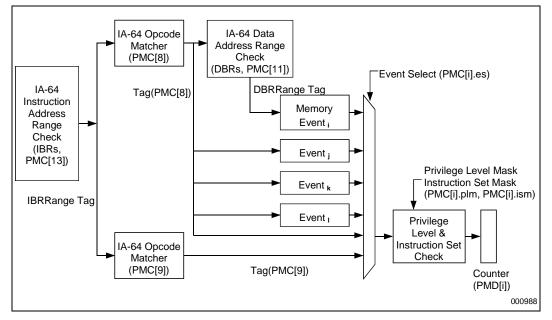

#### Figure 6-4. Itanium<sup>™</sup> Processor Event Qualification

# 6.1.3.1 Combining Opcode Matching, Instruction, and Data Address Range Check

The Itanium processor allows various event qualification mechanisms to be combined by providing the instruction tagging mechanism shown in Figure 6-5. Instruction address range check and opcode matching are available only for IA-64 code; they are disabled when IA-32 code is executing.

#### Figure 6-5. Instruction Tagging Mechanism in the Itanium™ Processor

During IA-64 instruction execution (PSR.is is zero), the instruction address range check is applied first. The resulting address range check tag (IBRRangeTag) is passed to two opcode matchers that combine the instruction address range check with the opcode match. Each of the two combined tags (Tag(PMC[8]) and Tag(PMC[9])) can be counted as a retired instruction count event (for details refer to event description IA64\_TAGGED\_INSTRS\_RETIRED in Table 7-3 "Instruction Issue and Retirement Events" on page 7-2).

One of the combined IA-64 address range and opcode match tags, Tag(PMC[8]), qualifies all down-stream pipeline events. Events in the memory hierarchy (L1 and L2 data cache and data TLB events) can further be qualified using a data address DBRRangeTag).

As summarized in Table 6-3, data address range checking can be combined with opcode matching and instruction range checking on the Itanium processor. Additional event qualifications based on the current privilege level and the current instruction set can be applied to all events and are discussed in Section 6.1.3.2, "Privilege Level Constraints" and Section 6.1.3.3, "Instruction Set Constraints".

#### Table 6-3. Itanium™ Processor Event Qualification Modes

| Event Qualification Modes                              | Instr. Address<br>Range Check<br>PMC[13].ta | Opcode Matching<br>PMC[8] | Data Address<br>Range Check<br>PMC[11].pt |

|--------------------------------------------------------|---------------------------------------------|---------------------------|-------------------------------------------|

| Unconstrained Monitoring (all events)                  | 1                                           | Oxffff_ffff_ffff_ffff     | 1                                         |

| Instruction Address Range Check only                   | 0                                           | Oxffff_ffff_ffff_ffff     | 1                                         |

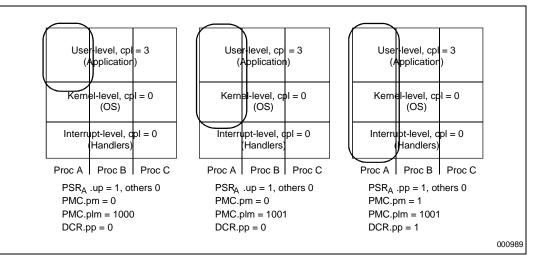

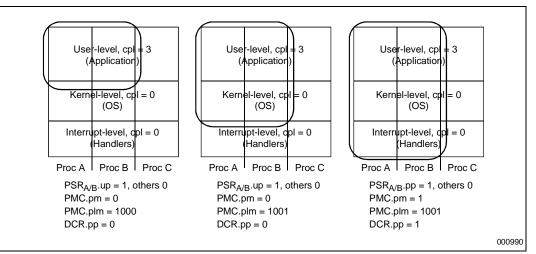

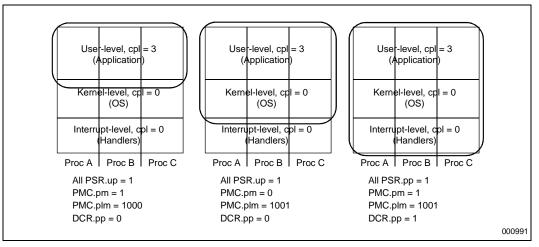

| Opcode Matching only                                   | 1                                           | Desired Opcodes           | 1                                         |